# Company update, HPC User Forum

Craig Prunty

VP Marketing & Biz Dev

(craig.Prunty@sipearl.com)

06-07 Sept 2023

#### SiPearl in a nutshell

Building the European energy-efficient HPC microprocessor

ecosystem

#### **Fabless**

Manufactured by TSMC, WW leader for advanced manufacturing nodes

#### Identified customers

Server manufacturers for targeted end users (governments, supercomputing centres, academics, industries, etc.)

# -SiPearl Origin

#### September 2018

Launch of the EuroHPC Joint Undertaking backed by a €8bn budget to deploy in Europe a world class exascale supercomputing infrastructure

#### December 2018

Launch of a call for proposals in 2017 for developing a new generation of high-end European microprocessors

- Budget: €150m

- Target: high-performance and energy-efficiency

Coordinated by Bull (Atos Group), the European Processor Initiative (EPI) consortium won this call for proposals. It has currently 28 members:

- Scientists: research institutes, universities and supercomputing centres

- Industry: European leaders, IT, electronics and automotive specialists

#### June 2019

SiPearl is the private company created within the EPI to launch a strategic industry for Europe.

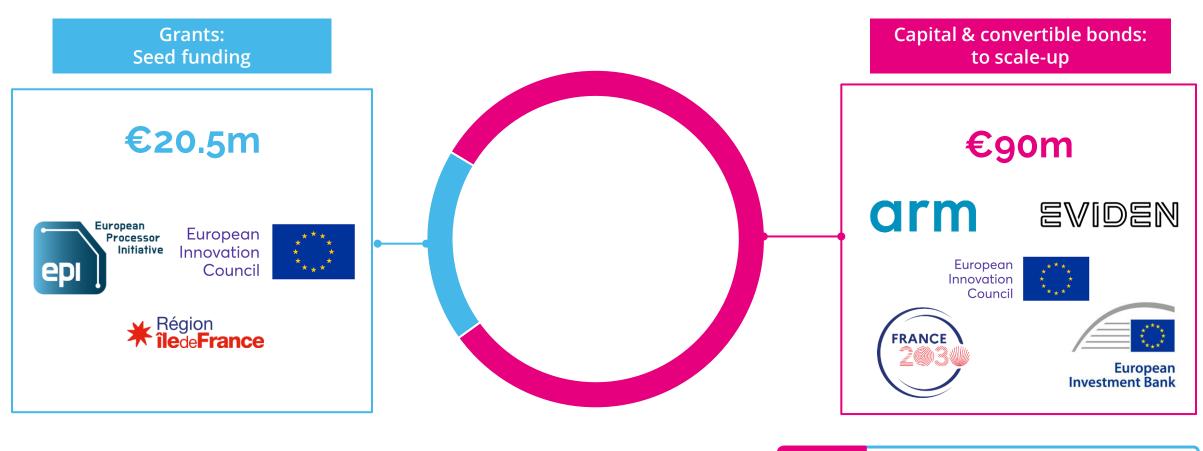

# -SiPearl's financing since its launch: €110.5m

Additional investors to join the round by end of 2023.

# SiPearl Key Partnerships

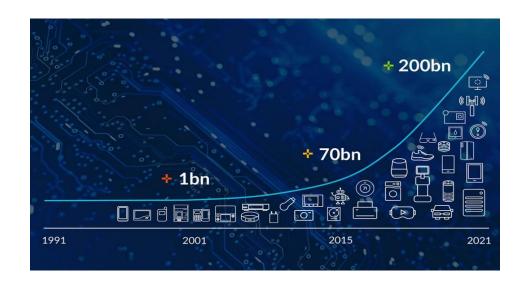

- Most widely used ISA on the planet, over 200bn Arm devices WW

- Low power high performance alternative to x86

- Arm design and modelling tools → time to market

- Arm toolchain and libraries

- Fully fleshed ecosystem is growing organically across HPC, Cloud;

Edge, IOT, Automotive

- Consortium funded by EU Government to foster a Sovereign EU based Server Processor & Ecosystem

- 27 funded partners across HPC Labs, System Integrators and OEMs, HW and SW companies

# -SiPearl Corporate Vision and Strategy

#### **HPC Supercomputing**

SiPearl entry business: European HPC

# HPCdedicated

#### Data center-Central

Data centers, private and public cloud

# Public cloud Private cloud DATA CENTER Embedded Security channel 6G infrastructure

#### Data center-Edge

Smaller Data centers, including around 6G infrastructure

# World leading industrial partnerships

#### Our ecosystem to accelerate Europe's adoption of exascale supercomputers

#### **Acceleration specialists**

Instinct<sup>™</sup> accelerators with ROCm<sup>™</sup> open software

Intelligence Processing Unit (IPU), designed to support artifical intelligence workloads

GPU Ponte Vecchio with the open unified software stack oneAPI

Portfolio of world-leading accelerated computing and networking solutions

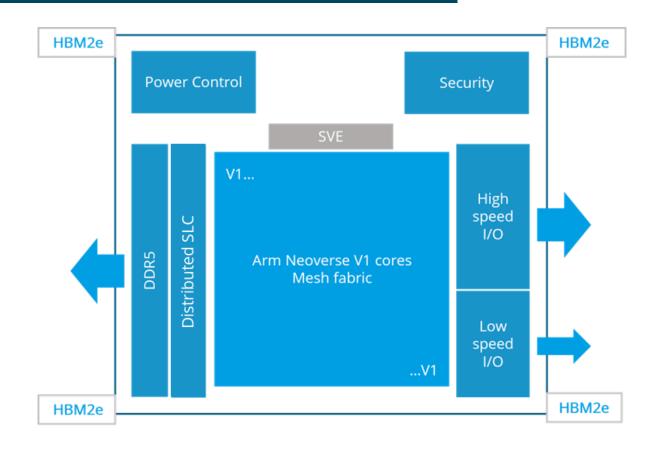

# –Rhea, our 1<sup>st</sup> generation microprocessor

With its high-performance energy-efficient Arm Neoverse V1 architecture, Rhea will meet the needs of all supercomputing workloads.

| Core                      | - Arm Architecture Neoverse V1 cores<br>- SVE 256 per core supporting 64/32/BF16 and int8<br>- Arm Virtualization Extensions                          |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| SoC                       | - Arm Mesh fabric  - Advanced RAS support including Arm RAS extensions  - Link protection for NOC and high-speed IO - ECC support for selected memory |

| Cache                     | - RAS supported for all Cache levels                                                                                                                  |

| Memory                    | ECC for memory and link protection for controllers - HBM2e - DDR-5                                                                                    |

| High Speed I/O            | PCIe or CCIX/CXL: root and endpoint support                                                                                                           |

| Other I/O                 | USB, GPIO, SPI, I <sup>2</sup> C                                                                                                                      |

| Power<br>Management       | Power management block to optimize perf/watt across use cases and workloads.                                                                          |

| Security Block<br>Support | - Secure boot and secure upgrade<br>- Crypto<br>- True Random Number Generation                                                                       |

Rhea will deliver extraordinary compute performance and efficiency with a superior Byte/Flop ratio.

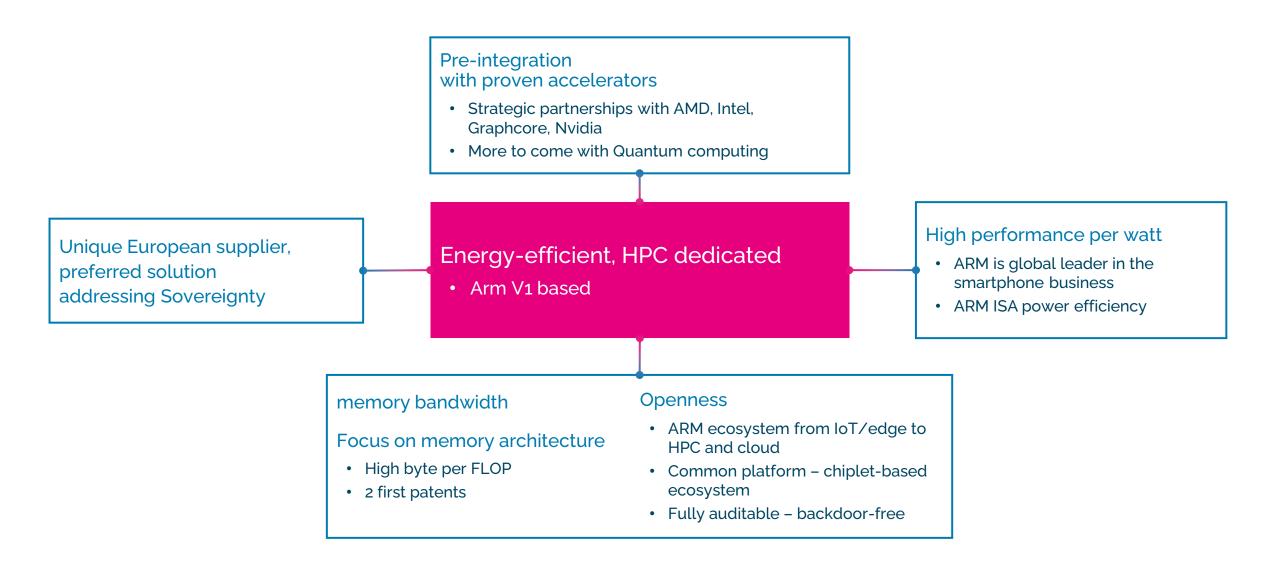

### -Rhea: differentiating factors

#### -Rhea in a nutshell

The world's first energy-efficient HPC-dedicated microprocessor designed to work with any third-party accelerator: GPU, artificial intelligence, quantum

#### Sovereignty

To further Europe's technological leadership and independence.

#### High Performance

To surpass the performance of 2,000,000 laptop computers.

#### **Energy-efficiency**

To halve power consumption for equivalent computing power.

#### Flexibility

Designed to work with any third-party accelerator (GPU, artificial intelligence, quantum).

#### Backdoor-free security

To protect data with secure end-to-end network transmission.

# EU SW preparation and porting

#### **COE FOR HPC APPLICATIONS**

Advancing Lighthouse Applications addressing scientific grand challenge(s) where exascale performance is needed.

| Project      | Topic                                                            | Organisation                            |

|--------------|------------------------------------------------------------------|-----------------------------------------|

| MAX          | Material science SW prep for exascale class systems              | CONSIGLIO NAZIONALE DELLE RICERCHE (IT) |

| EXCELLERAT   | Engineering and Manufacturing SW prep for exascale class systems | UNIVERSITY OF STUTTGART (DE)            |

| PLASMA-PEPSC | High-energy physics SW prep for exascale class systems           | KTH (SE)                                |

#### **OPEN CLOUD**

Advance SW and HW interfaces between the processing architectures and cloud applications focusing on industry standards and Open-source stacks.

| Project  | Topic                                                                                                                                   | Organisation                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| RISER    | OS SW port to EU Risc-V cloud server infrastructure                                                                                     | IDRYMA TECHNOLOGIAS KAI EREVNAS (GR)                 |

| OPENCUBE | develop a full-stack European Cloud computing blueprint deployed on European hardware infrastructure.                                   | KTH (SE)                                             |

| AERO     | open-source software including OS, compilers, runtimes, system software and auxiliary software deployment services for cloud computing. | INSTITUTE OF COMMUNICATION AND COMPUTER SYSTEMS (GR) |

#### About... SiPearl

SiPearl is building the first energy-efficient HPC-dedicated microprocessor designed to work with any third-party accelerator (GPU, artificial intelligence, quantum). This new generation of microprocessors will first target EuroHPC Joint Undertaking ecosystem, which is deploying world-class supercomputing infrastructures in Europe for solving major challenges in medical research, artificial intelligence, security, energy management and climate while reducing its environmental footprint.

SiPearl is working in close collaboration with its 27 partners from the European Processor Initiative (EPI) consortium - leading names from the scientific community, supercomputing centres and industry - which are its stakeholders, future clients and end-users.

SiPearl employs 130 people in France (Maisons-Laffitte, Grenoble, Massy, Sophia Antipolis), Germany (Duisburg) and Spain (Barcelona).

#### Media contact:

Marie-Anne Garigue / Grégory Bosson + 33 6 09 05 87 80 / + 33 6 60 75 71 61 marie-anne.garigue@sipearl.com gregory.bosson@sipearl.com