HPC USER FORUM PRESENTATION,

RESTON, 2024

Decisions and Predictions at the Speeds of Relevance at the Edge or in the Cloud

Arun Majumdar, CEO

# Permion Company

Decisions and Predictions at Speeds of Relevance from Edge to Cloud

A US-built Virtual Al Processor, On-Premise or In-Cloud, Performance Increase, Reduce Costs, and Mitigate Risks to Al use: Zero-Hallucination, Interoperable, Trustworthy, Neural and Graph Al/ML.

#### Company

- o Founded 2018

- o 150,000 Developer hours

- o US team & AI technology

#### Innovations

- Trustworthy Al

- Works with Legacy and 3<sup>rd</sup> Party

- o SDK, Python, Java, C++, APIs

#### **Credibility**

- US Government Contracts

- o Leidos Inc .partner for DoD

- o IC/DoD Past Performance

#### Offering

- o Al Apps on-site or cloud

- Al Tools and SDK

- o Experienced Team

It's not the size of the dog in the fight, it's the size of the fight in the dog - Eisenhower

# Our Mission is to Create the Foundations for Technological Superiority

To Ignite the Innovations of Tomorrow

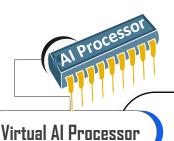

## Representative Relative Problem Complexity for Al Algorithms

Performance of Processing Complexity

**Non-Von Neumann Instruction Set Architecture Designed for Edge & HPC**

**Artificial Intelligence**

Designs

Neural, Graph, Symbolic, **Hybrid Designs**

Analog, Photonic, Quantum, Hybrid

**Physical** Hardware

Software Defined Compute – Data Oriented Design – Software Defined Hardware

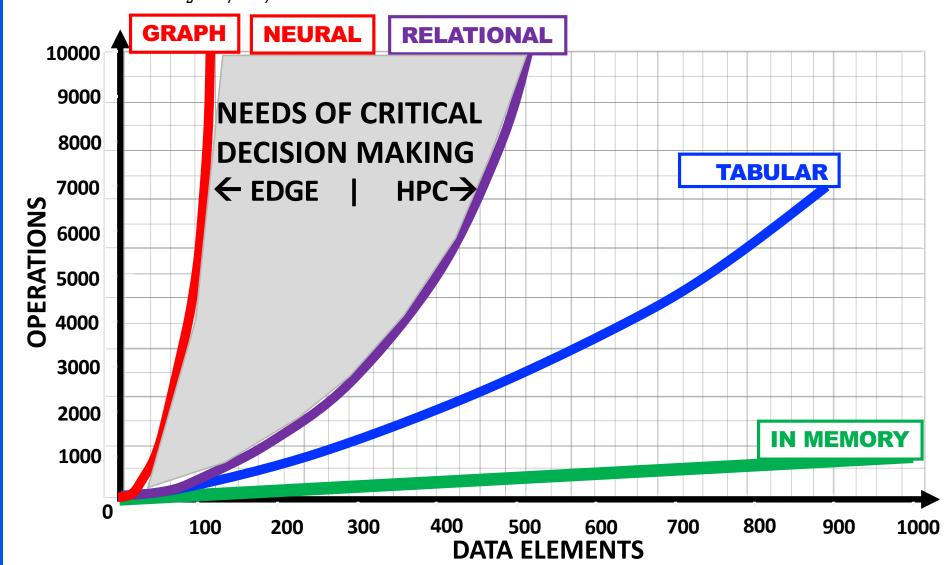

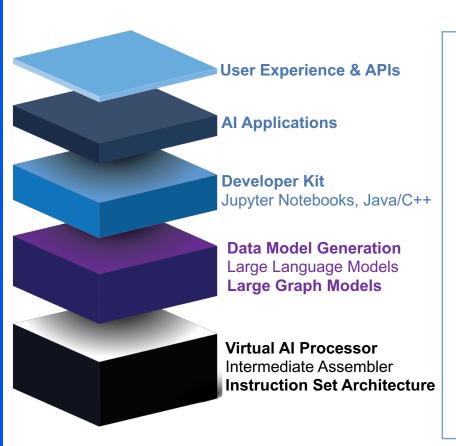

## Virtual Al Processor – Design Philosophy for Edge-to-HPC

X-Machines Theory, Data Oriented Computing (DoC)

- 1. Single target code generation Al Virtual Instruction Set Architecture (ISA)

- Instruction Set Architecture based on X-Machine Theory ("Category Theory")

- CPU, GPU, TPU, DPU, RISC-V, ... future hardware

- 2. Portable binaries and mobile Al computation process data at its origin

- LLVM and Intermediate Assembler JIT Compilation

- C++14 Micro-architecture Implementation (for <u>legacy</u> compatibility)

- 3. Support for diverse compiled languages Software and Hardware for Al

- Verilog, VHDL, direct to silicon (FPGA) & ASICs

- Graph (OpenCypher, GraphQL, ...) & future Quantum Languages

- 4. Interactive tradeoffs in compute fine grain control of Al computing models

- Data Plane & Execution Plane Interaction can reshape computations

- Control Plane meta-control (i.e., code as data and data as code)

- 5. An open and extensible modular Al foundation For more complex systems

## **Permion Al Platform**

Interoperates and works on-premise and in cloud, from Legacy to all current third-party systems, and ready for future hardware

- US built Neuro-Symbolic ISA as Virtual AI Processor

- High Fidelity explainable reasoning Edge to Cloud

- Industrial-scale AI/ML (Low Latency) Performance

- Can run on legacy, existing, and emerging platforms

- Large Graph Models, Large Language Models

- ISO Standards Compliant (ISO 24707, ISO 13211)

- Advanced Graph Generative Al

- Cheaper, Faster, Better, Scalable, Affordable

Trustworthy: explainable, meaningful, explanation accuracy, and knowledge limits

# **Contacts**

### **Address**

8000 Towers Crescent, Suite 1350, Vienna, VA 22182 (Tyson's Corner)

## **Email Addresses**

<u>arun@permion.ai</u> jgavrilis@permion.ai

## **Cell-Phones**

Arun M: (571) 344-0521 Jim. G: (910) 922-9261